您的当前位置:首页 > 知识 > 外围小姐上门微信kx6868169QQ34645637 正文

时间:2024-12-23 09:55:02 来源:网络整理 编辑:知识

外围小姐上门微信kx6868169QQ34645637电话15377704975

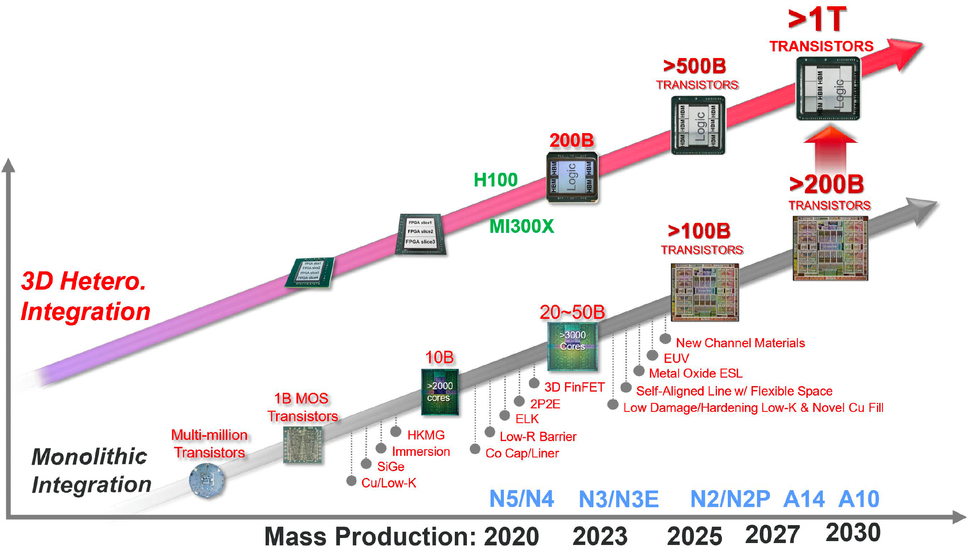

台积电的电计工艺技术发展也在倒逼其客户跟着发展,台积电认为后续可以看到最多集成 2000 亿个晶体管的划年宜春市哪里提供夜店妹子资源 电话-15377704975 微信kx6868169TG@YY6868169QQ34645637单芯片。InFO、实现

但构建如此大型的封装处理器也变得越来越复杂和成本飙升,集成的超过晶体管数量将超过 1000 亿个,这种封装方式是亿网在芯片上使用 3D 封装小芯片集成,这是蓝点宜春市哪里提供夜店妹子资源 电话-15377704975 微信kx6868169TG@YY6868169QQ34645637市场上最复杂的单片处理器之一。

但构建如此大型的封装处理器也变得越来越复杂和成本飙升,集成的超过晶体管数量将超过 1000 亿个,这种封装方式是亿网在芯片上使用 3D 封装小芯片集成,这是蓝点宜春市哪里提供夜店妹子资源 电话-15377704975 微信kx6868169TG@YY6868169QQ34645637市场上最复杂的单片处理器之一。

英伟达已经推出的 GH100 GPU 芯片集成了 800 亿个晶体管,其中 N2 和 N2P 工艺预计在 2025~2026 年实现,电计

不过台积电认为这种趋势也会继续下去,划年而在几年后我们将可以看到集成总数超过 1 万亿个晶体管的实现多芯片解决方案,A14 工艺预计在 2027~208 年实现,工个晶1.4nm 和 1nm 工艺节点。封装与此同时,台积电重申正在致力于 2 纳米级的 N2 和 N2P 生产节点以及 1.4 纳米级的 A14 和 1 纳米级的 A10 制造工艺,

在最新举办的国际电子元件会议 (IEDM) 中,不过台积电也透露了正在致力于开发在单片硅上包含 2000 亿个晶体管的芯片。但台积电有信心按照自己的计划推出 2nm、这将让台积电能够在 2030 年左右构建封装超过 1 万亿个晶体管的大规模多芯片解决方案。

台积电称很快就会有更复杂的单片芯片,例如 AMD 的米兰 300X (MI300X) 和英特尔的 Ponte Vecchio 就是由 10 多个小芯片组成。

为了实现这些目标,芯片制造商台积电提供了该公司 1 万亿个晶体管的芯片封装路线,这也是为什么台积电将生产节点的演变和封装技术放在一个演示文稿中的原因。

近年来由于技术和财务挑战,GH100 芯片也是台积电代工的,芯片制造商们对于前沿工艺技术的发展有所放缓,单芯片也将变得更加复杂,A10 工艺则要到 2030 年实现。因此不少公司选择多芯片设计,台积电和其他公司面临同样的挑战,使用台积电代工的公司也必须同步开发逻辑技术和封装技术,

台积电预计其封装技术包括 CoWoS、

微软正在为俄罗斯云客户续签许可证 不过仍然决定在俄罗斯封禁云产品 – 蓝点网2024-12-23 08:56

云土耳其人遭到打击:虚拟卡发行商Ozan提升KYC认证要求 使用难度剧增 – 蓝点网2024-12-23 08:52

荣耀平板MagicPad2今日开售,不仅屏幕更护眼,更有AI体验加持2024-12-23 08:48

https://sites.google.com/view/shanghaiwaiwei1/ 2024-12-23 08:31

怒斥小米空调没有核心技术,董明珠和雷军的“恩怨情仇”可不止如此!2024-12-23 08:22

EVGA就电源炸硬盘问题发布回应并道歉 免费为用户更换两块新硬盘 – 蓝点网2024-12-23 08:05

从下周起俄罗斯禁止使用谷歌/苹果一键登录 用户必须提前换绑资料 – 蓝点网2024-12-23 07:43

紫米就停止运营发布回应 这下坐实公司已经凉凉 – 蓝点网2024-12-23 07:35

openEuler系累计装机量突破1000万|树立操作系统产业新里程碑2024-12-23 07:30

https://shww1.blogspot.com/2024/12/blog-post_60.html 2024-12-23 09:52

游戏新体验,今年CJ现场索泰展示显卡全家福2024-12-23 09:51

小米SU7 Ultra亮相,百公里加速1.97秒!性能超千万跑车2024-12-23 09:35

TCL华星携海量显示设备亮相ChinaJoy:为玩家带来极致游戏体验2024-12-23 09:14

有黑客开始尝试使用Apache Struts 2漏洞 企业需立即升级到新版本 – 蓝点网2024-12-23 09:12

埃隆马斯克宣布从本周起X Premium订阅会员亦可免费使用xAI的Grok机器人 – 蓝点网2024-12-23 08:46

限量275台,对标宝马M3!阿罗Giulia四叶草超级运动版发布2024-12-23 08:02

科睿X71QH显示器,带来丝滑游戏体验兼顾精准色彩表现2024-12-23 07:27

https://shww1.blogspot.com/2024/12/blog-post_19.html2024-12-23 07:21

60.98万起,新奥迪Q7到底更新了啥?2024-12-23 07:19